Seoul National University

of Science and Technology

232 Gongneung-ro, Nowon-gu,

01811, Seoul, KOREA

parkjoungmin

parkjoungmin seoultech.ac.kr

seoultech.ac.kr

parkjoungmin

parkjoungmin seoultech.ac.kr

seoultech.ac.kr

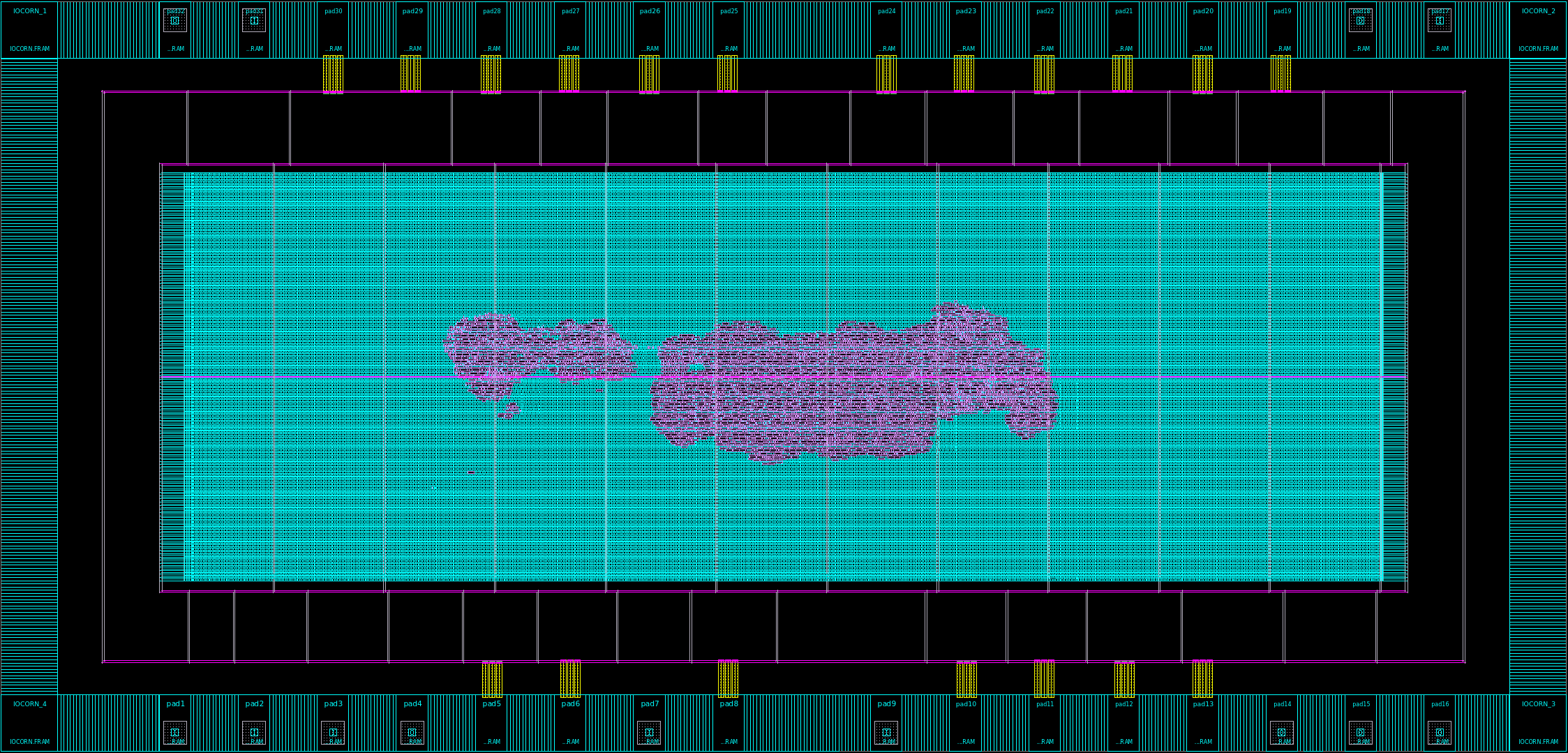

4. "A Reconfigurable AI Processor Executing Lightweight Algorithms for Sequential Data Applications"

Designer: Raehyeong Kim, Jinyoung Shin, Jinyeol Kim, Dayoung Lee, Joungmin Park and Seung Eun Lee

Technology: Samsung 28nm FD-SOI (1-Poly 10-Metal)

Tape Out: 2025. 09. 25

Operation Voltages: 1.1V/1.8V (Core/IO)

Clock Frequency: 100MHz (max)

Gate Counts: 360K @ 100MHz

Memory Size: 8Kb*256 (AI region)

Core Size: 4mm x 4mm

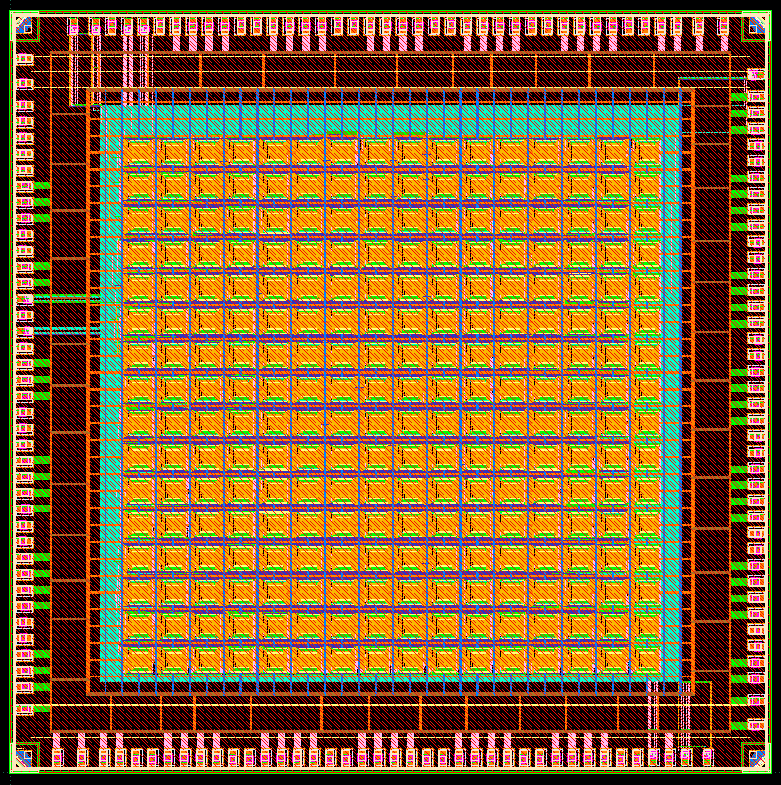

3. "A Networked Processor Array based on Heterogeneous Computing Units for AI Acceleration"

Designer: Seongmo Ahn, Joungmin Park, Jongwon Oh, Jaeseong Kim and Seung Eun Lee

Technology: Samsung 28nm LPP (1-Poly 10-Metal)

Tape Out: 2025. 07. 07

Operation Voltages: 1.0V/1.8V (Core/IO)

Clock Frequency: 100MHz (max)

Gate Counts: 468K @ 100MHz

Memory Size: 8Kb*4/8Kb*4/128Kb*4 (Code/Data/AI region)

Core Size: 4mm x 4mm

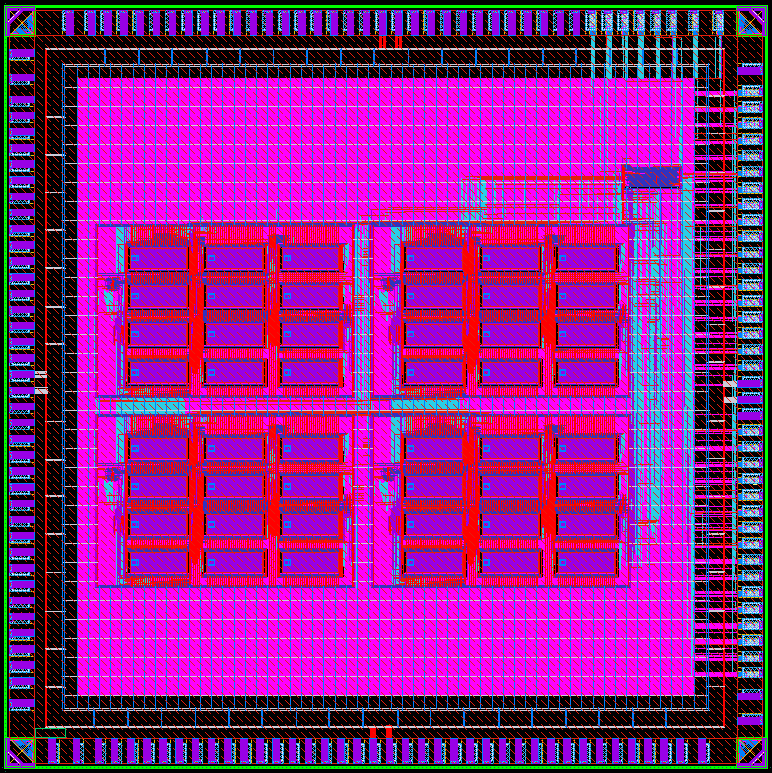

2. "A Internal Network IP for Next-Generation Robots with SPI"

Designer: kwanghyun Go, Joungmin Park, Jongwon Oh

Technology: DBHitek 180nm BCDMOS

Tape Out: 2024. 07. 22

Operation Voltages: 5.0V/1.8V (Core/IO)

Clock Frequency: 50MHz (max)

Gate Counts: 36K @ 50MHz

Core Size: 5mm x 2.5mm

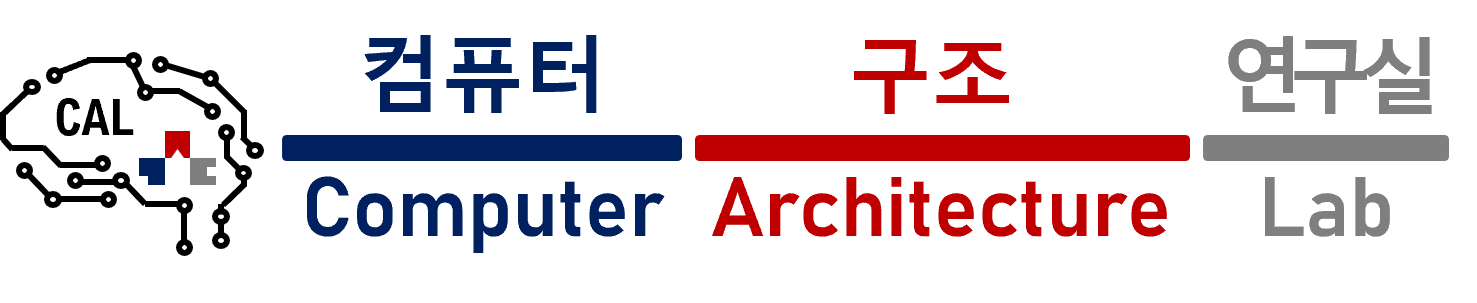

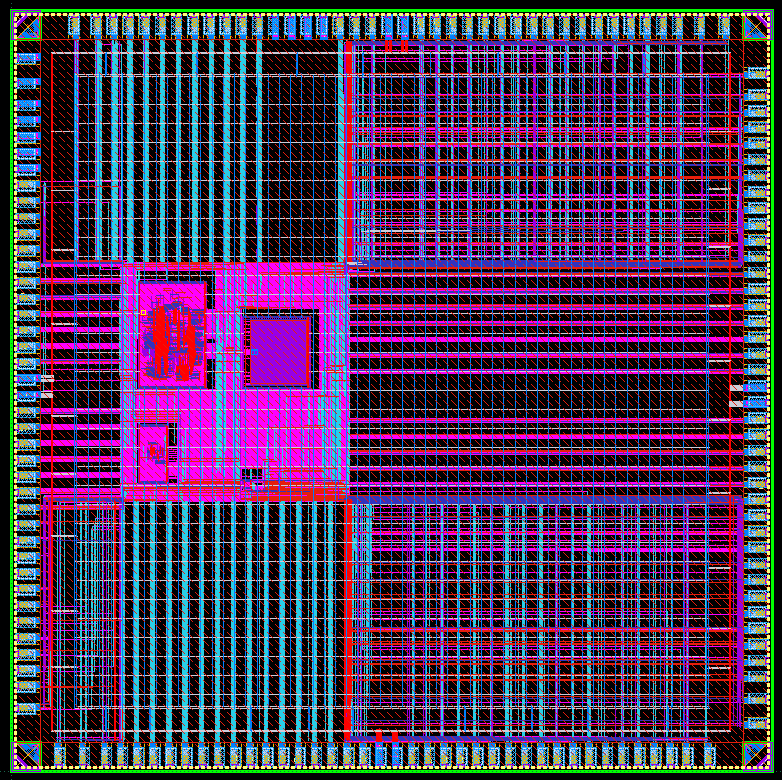

1. "CoFEx : Convolution-based Feature Extractor Equipped with an Improved Systolic Array Architecture"

Designer: Joungmin Park, Sangho Lee, Jinyoung Shin, Raegyeong Kim and Seung Eun Lee

Technology: Samsung 28nm LPP (1-Poly 10-Metal)

Tape Out: 2024.07.18

Operation Voltages: 1.0V/1.8V (Core/IO)

Clock Frequency: 50MHz (max)

Gate Counts: 245K @ 50MHz

Memory Size: 512Kb (AI region)

Core Size: 4mm x 4mm